이종 반도체 연결 차세대 기술

UCIe 규격 적용…상용화 임박

양산땐 파운드리 시장 주도권

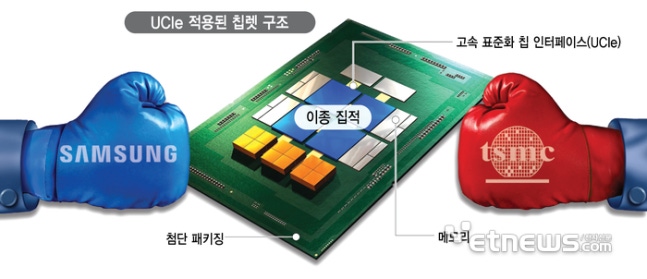

삼성전자와 TSMC 간 '칩렛' 양산 승부가 시작됐다. 칩렛은 서로 다른 반도체(다이)를 연결하는 차세대 반도체 제조 기술이다. 삼성전자와 TSMC 모두 올 상반기 중 칩렛 표준인 'UCIe' 기반 반도체 상용화를 추진 중이다. 표준 규격의 칩렛은 아직 상용화된 적 없어 양산에 성공하는 기업이 시장을 선점할 가능성이 있다.UCIe 규격 적용…상용화 임박

양산땐 파운드리 시장 주도권

18일 업계에 따르면 삼성전자와 TSMC는 UCIe를 적용한 반도체 시제품의 테이프아웃을 완료하고 올해 상반기 중 검증을 마칠 계획인 것으로 파악됐다. 테이프아웃은 반도체 설계가 완성됐다는 뜻으로, 이제 생산 단계로 넘어간다는 의미다.

UCIe는 반도체 업계에서 주목받는 칩렛 표준이다. 그동안 각 반도체 기업마다 서로 다른 기술로 반도체를 연결했는데, 호환성과 효율성을 강화하기 위해 표준이 만들어졌다. 삼성전자·TSMC·인텔·퀄컴·MS·구글 등이 개방형 칩렛 표준화를 목표로 2022년 3월 UCIe 컨소시엄을 출범시켰으며, 현재 UCIe 1.1까지 마련된 상태다.

표준 규격은 있지만 UCIe 기반 반도체는 아직이다. 반도체를 만드는 제조 공정, 즉 UCIe에 최적화된 공정을 새로 개발해야 해서다. 삼성전자와 TSMC는 UCIe 기반 칩렛 공정 개발을 위해 반도체 설계자산(IP) 기업인 시높시스와 케이던스와 협력했고, 이제 상용화 및 양산이 막바지에 이른 것으로 파악됐다. 구체적인 고객사는 확인되지 않았지만 삼성전자는 5나노미터(㎚) 이하 선단 공정을, TSMC는 5나노 공정을 활용해 UCIe 기반 칩렛을 상용화할 것으로 전해졌다.

표준 칩렛 상용화에 관심이 쏠리는 건 칩렛 기술의 폭발적인 성장이 예상돼서다. 칩렛은 중앙처리장치(CPU)·그래픽처리장치(GPU) 같은 시스템 반도체와 D램 메모리 등 서로 다른(이종) 반도체를 마치 하나의 반도체인 것처럼 연결하는 것이다.

반도체 성능을 최대한으로 끌어올리기 위해 탄생한 기술로, 반도체 미세화의 한계를 극복할 대안으로 주목 받으며 급부상했다. 특히 최근 GPU와 고대역폭메모리(HBM)를 결합하는 AI 반도체 시대가 열리면서 칩렛이 떠올랐다.

칩렛은 여러 반도체를 연결하는 구조 때문에 그동안 패키징 영역으로 분류됐다. 하지만 실제로는 반도체 IP 개발부터 칩 설계, 제조, 패키징 등 반도체 전주기와 연관 깊어 처음서부터 설계와 파운드리 회사 간 협력이 필수다.

표준 칩렛을 생산할 수 있는 능력은 곧 차세대 반도체 시장을 주도할 수 있는 핵심 기반이 된다. 칩렛이 활성화될 수록, 표준은 늘어나고 이를 양산할 수 있는 파운드리 업체로 주문이 몰리기 때문이다. 세계 최대 파운드리 업체인 TSMC와 파운드리 사업 강화를 천명한 삼성전자가 UCIe 공정을 준비하는 이유다.

반도체 업계 관계자는 “수많은 반도체 기업이 UCIe에 기반을 둔 칩 설계로 전환하려하고 관련 기술 개발을 준비하고 있다”며 “삼성과 TSMC의 시제품 개발이 UCIe 생태계 성공을 가늠하는 척도가 될 것”이라고 전망했다.