삼성전자와 TSMC가 차세대 첨단 패키징 기술을 두고 맞붙는다. 양사 모두 인공지능(AI) 반도체 완제품을 만드는 패키징으로 '팬아웃-패널레벨패키징(FO-PLP)' 기술을 차기 로드맵으로 낙점했는데, 핵심 소재·부품을 달리해 누가 우위를 점할지 주목된다.

18일 업계에 따르면 삼성전자와 TSMC는 각기 서로 다른 소재로 AI 등 고성능컴퓨팅(HPC)용 패키징을 준비하는 것으로 알려졌다. 삼성은 기존 인쇄회로기판(PCB)에 쓰는 '플라스틱(오거닉)'을, TSMC는 '유리'를 패널로 활용하는 방안이 유력하다. 패널은 반도체(다이)를 지지하는 역할을 하며 패키징을 용이하게 할 수 있도록 하는 핵심 구성 요소다.

패키징 업계 관계자는 “차세대 AI 반도체에 적용할 첨단 패키징 기술에 대해 삼성전자와 TSMC 모두 FO-PLP를 준비하지만, 패널 소재는 서로 다른 것을 검토 중”이라며 “플라스틱이냐 유리냐에 따라 성능과 공정 차이가 발생하는 만큼, 패키징 사업 성과도 달라질 수 있다”고 말했다.

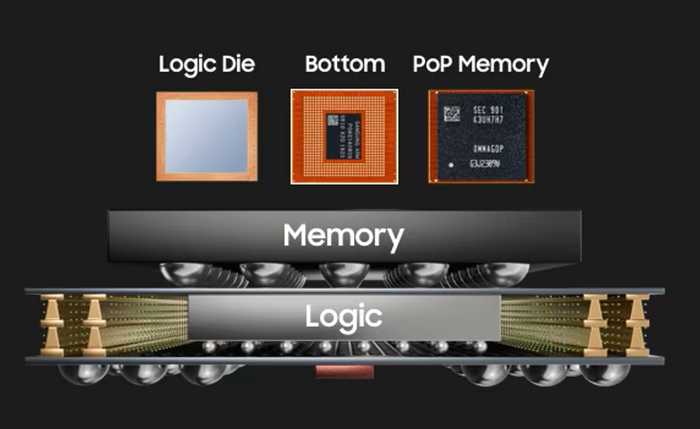

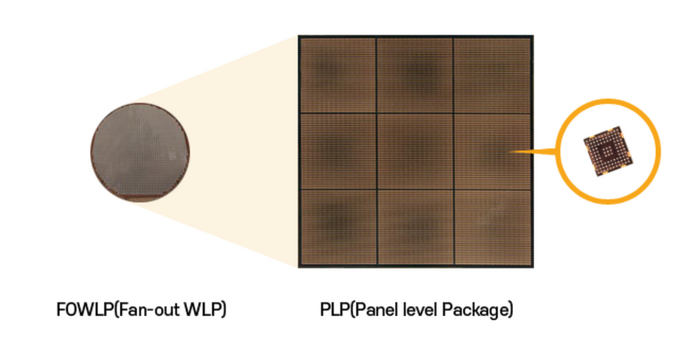

FO-PLP는 회로를 구현한 반도체(다이)를 사각 패널 위에서 패키징하는 기술이다. 웨이퍼 위에서 패키징하는 웨이퍼레벨패키징(WLP)과 대비된다. FO-PLP는 둥근 웨이퍼 대신 사각 패널에서 공정을 진행, 모서리에 버리는 칩이 없어 생산성을 높일 수 있다. 600×600㎜ 패널 기준으로 같은 칩을 생산하면 300㎜(12인치) 웨이퍼 대비 5~6배 많은 칩을 만들 수 있다.

FO-PLP 패널은 주로 플라스틱 소재를 써왔다. FO-PLP 강자는 삼성전자로, 2019년 삼성전기로부터 FO-PLP 사업을 인수한 후 모바일 애플리케이션프로세서(AP)·전력관리반도체(PMIC) 패키징에 활용해왔다. 삼성 FO-PLP는 초기부터 플라스틱 패널을 써왔던 만큼 관련 설비 투자를 최소화하고 기술 노하우를 이어가기 위해 이같은 전략을 유지할 것이란 게 중론이다. 삼성전자는 지난해부터 AVP 개발팀 주도로 관련 연구개발(R&D)에 착수했다.

반면, TSMC는 유리 패널을 검토하는 것으로 알려졌다. 현재 TSMC는 CoWoS라는 2.5D 패키징 기술로, 엔비디아 등 AI 반도체를 패키징 중이나 생산능력 한계와 비용 문제로 FO-PLP를 준비하고 있다. FO-PLP는 고가의 인터포저를 사용하지 않아 CoWoS와 견줘 비용 효율적인 것으로 알려졌다.

TSMC가 지난 8월 대만 디스플레이 패널 제조사 이노룩스의 LCD 공장 일부를 인수한 것도 FO-PLP 라인을 구축하기 위한 것으로 분석된다. 유리 패널 관련 이노룩스와의 기술 협력도 예상된다. 시장조사업체 트렌드포스에 따르면, TSMC는 현재 엔비디아와 AMD AI 가속기를 위한 FO-PLP 기술을 평가 중이다. 2027년 FO-PLP 양산에 돌입할 것으로 알려졌으나 최근 시점을 앞당길 것이란 관측도 나온다.

유리를 FO-PLP 패널로 쓸 경우 이물(파티클)이나 패널 휨(워피지) 이슈에서 좀 더 유리한 것으로 평가받는다. 다만 유리를 다루기 어려운만큼 공정 난도가 높다.

또 다른 반도체 업계 관계자는 “삼성전자와 TSMC가 다른 FO-PLP 소재 전략에서 취했지만, 소재 특성과 공정 경험도 다르기 때문에 누가 경쟁 우위를 차지할지는 속단하기 이르다”며 “양산 시 수율과 성능에 따라 AI 반도체 시장 판도가 달라질 수 있을 것”이라고 말했다.